Introduction to Model Checking

Winter term 08/09

## – Series 1 –

Hand in on October 31 before the exercise class.

## Exercise 1

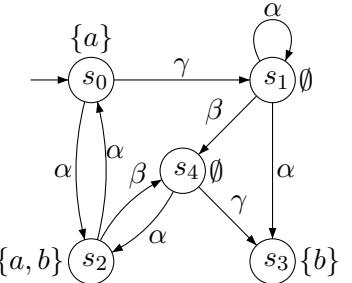

We consider the basic definitions for transition systems. Let  $TS$  be the transition system depicted on the right.

- Give the formal definition of  $TS$ .

- Specify a finite and an infinite execution of  $TS$ .

- Decide whether  $TS$  is an *AP*-deterministic or an action-deterministic transition system. Justify your answer!

(0.5, 0.5, 1 points)

## Exercise 2

A concurrent system comprises  $P_1, \dots, P_n$  competing processes (without shared memory) that access common resources within their critical sections. We assume that the resources may only be accessed exclusively and that  $k$  equivalent instances are available.

Further, let  $n, k \in \mathbb{N}$  with  $2 \leq k \leq n$ .

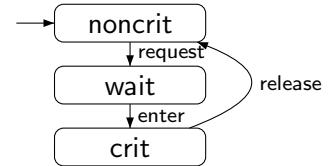

Process  $P_i$  can be described by a transition system  $TS_i$  with three states and the actions *request*, *enter*, and *release* as indicated on the right.

(1 + 2 points)

$TS_i :$

- Develop a transition system representation of an arbiter that communicates with the processes using actions *request* and *release*. The arbiter should assure that there are no more than  $k$  processes within their critical section at the same time.

- Sketch the transition system of the parallel composition

$$(TS_1 \parallel TS_2 \parallel TS_3) \parallel_{Syn} \text{Arbiter}$$

with  $Syn = \{\text{request}, \text{release}\}$  for  $k = 2$ . You need not consider the states  $wait_i$ .

### Exercise 3

(2 + 2 points)

Consider the following mutual exclusion algorithm that uses the shared variables  $y_1$  and  $y_2$  (which are initially both 0):

Process  $P_1$ :

```

while true do

... non-critical section ...

$y_1 := y_2 + 1$

wait until ( $y_2 = 0$ )  $\vee$  ( $y_1 \leq y_2$ )

... critical section ...

$y_1 := 0$

... non-critical section ...

od

```

Process  $P_2$ :

```

while true do

... non-critical section ...

$y_2 := y_1 + 1$

wait until ( $y_1 = 0$ )  $\vee$  ( $y_2 < y_1$ )

... critical section ...

$y_2 := 0$

... non-critical section ...

od

```

Questions:

- Give the program graph representation of both processes.

(A pictorial representation suffices)

- Give the reachable part of the transition system of  $P_1 \parallel P_2$  where  $y_1 \leq 2$  and  $y_2 \leq 2$ .

### Exercise 4

(2 + 3 points)

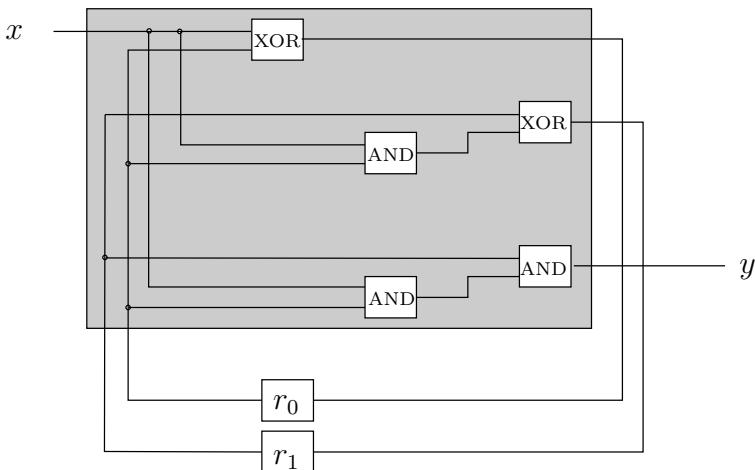

The circuit  $C_1$  describes the layout of a hardware adder that stores a 2-bit binary number represented by the registers  $r_0$  and  $r_1$ . In each cycle, the value of  $x$  is added to the currently stored value;  $y$  is used as the carry bit:

$C_1$  :

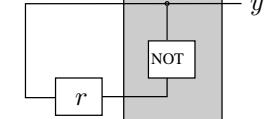

$C_2$  :

- Give the transition system representation  $TS_1$  of the circuit  $C_1$ .

- Let  $TS_2$  be the transition system of the circuit  $C_2$ .

Outline the transition system  $TS_1 \otimes TS_2$ .